www.afm-iournal.de

# A Graphene-Based Vacuum Transistor with a High **ON/OFF Current Ratio**

Gongtao Wu, Xianlong Wei,\* Zhiyong Zhang, Qing Chen, and Lianmao Peng

A graphene-based vacuum transistor (GVT) with a high ON/OFF current ratio is proposed and experimentally realized by employing electrically biased graphene as the electron emitter. The states of a GVT are switched by tuning the bias voltage applied to the graphene emitter with an ON/OFF current ratio up to 10<sup>6</sup>, a subthreshold slope of 120 mV dec<sup>-1</sup> and low working voltages of <10 V, exhibiting switching performances superior to those of previously reported graphene-based solid-state transistors. GVTs are fabricated and integrated using silicon microfabrication technology. A perfectly symmetric ambipolar device is achieved by integrating two GVTs, implying the potential of realizing vacuum integrated circuits based on GVTs. GVTs are expected to find applications in extreme environments such as high temperature and intense irradiation.

#### 1. Introduction

Graphene has attracted widespread research interest for its promising applications in high-performance electronic nanodevices due to its ultrahigh charge carrier mobility and the compatible fabrication scheme of its electronic devices with standard silicon microfabrication technology. Due to the lack of a bandgap, field effect transistors (FETs) with intrinsic graphene channel were found to have an ON/OFF current ratio of only less than 10 and could not be completely switched off, [1,2] suggesting that intrinsic graphene-based FETs are not suitable for integrated logic circuit applications. To this end, many efforts have been made to introduce an energy gap in graphene to overcome the switchless of its FETs, including fabricating narrow graphene nanoribbons,[3,4] chemical doping,[5] and applying a perpendicular electric field to a bilayer graphene. [2,6] However, the successful introduction of an energy gap in graphene in those efforts simultaneously sacrificed the carrier mobility of graphene due to the introduction of additional carrier scattering or the simplicity of graphene-based FET structures due to an additional required gate electrode. In addition to

the introduction of an energy gap in graphene, several alternative graphene device concepts have been proposed to achieve a high ON/OFF current ratio, including field-effect tunneling transistors based on vertical graphene heterostructures,[7-9] graphene barristors based on gate-controlled graphene/silicon Schottky barrier.[10] and graphene-based hot electron transistors.[11,12] Even though those new conceptual devices have been demonstrated to exhibit exceptional ON/OFF current ratios exceeding 10<sup>5</sup>–10<sup>6</sup>, their transitions between ON and OFF states are still slow with large subthreshold slopes far from the theoretical limit of conventional MOS (metal-oxide-semiconductor) FETs.

While charge carriers in previously reported graphene-based electronic devices transport in graphene channels or other solid-state mediums, electronic devices employing vacuum as the medium for charge transport have at least two advantages compared to those employing solid-state mediums. First, charge carriers transport freely in vacuum without any scattering and have a theoretical velocity of approaching  $3 \times 10^8 \ \text{m s}^{-1}$  in vacuum. Second, vacuum devices are immune to extreme environments such as high temperature and intense irradiation. However, vacuum electronic devices gave way to solid-state electronic devices in most application areas in the past decades because of the superior performances of semiconductor-based solid-state devices, e.g., lower cost, much smaller size, higher energy efficiency, higher reliability and consistency, and capability of large-scale integration, etc. It should be noted that, many of those advantages are associated with the advanced and mature semiconductor microfabrication technology, by which semiconductor-based solid-state devices are fabricated and integrated, and are not peculiar to solid-state devices. If vacuum devices can be fabricated and integrated using semiconductor microfabrication technology as well and their sizes can be shrunk to the micrometer or even nanometer scale, they are expected to possess the advantages of both conventional vacuum devices and solid-state ones. In this context, various field emission vacuum triodes/transistors fabricated on Si wafer by semiconductor microfabrication technology have been reported.[13-18] Recently, a couple of vacuum transistors working at the voltages comparable to those of solid-state transistors have been achieved. [19-21] However, the performances of these vacuum devices are still overshadowed compared to those of solid-state ones, especially for their low ON/OFF current ratio and slow transition between ON and OFF states.

G. Wu, Dr. X. Wei, Prof. Z. Zhang, Prof. Q. Chen, Prof. L. Peng Key Laboratory for the Physics and Chemistry of Nanodevices Department of Electronics **Peking University** Beijing 100871, P. R. China

www.MaterialsViews.com

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

In this paper, we propose a graphene-based vacuum transistor (GVT) by employing an electrically biased graphene as the electron emitter and successfully realize it in experiments. The states of a GVT can be switched by tuning the bias voltage applied to the graphene emitter with an ON/OFF current ratio up to 10<sup>6</sup> and a subthreshold slope of 120 mV dec<sup>-1</sup>, superior to those of previously reported graphene-based solid-state devices. Moreover, GVTs work at low voltages of less than 10 V, comparable to those of graphene-based solid-state devices, and they can be fabricated and integrated using silicon microfabrication technology. To demonstrate the integration of GVTs, an ambipolar device with perfectly symmetric ambipolar transfer characteristics is realized by integrating two GVTs, implying the potential of GVTs to possess the advantages of both conventional vacuum devices and solid-state ones, and to be used for vacuum integrated circuits.

## 2. Results and Discussion

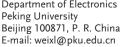

The structure of a GVT and its working principle are schematically shown in Figure 1a,b. It can be seen that our proposed GVT has a simple structure resembling to that of a graphene-based back-gate FET (GBBGFET) fabricated on a SiO<sub>2</sub>/Si substrate (Figure 1c,d), [3] except that the dielectric layer underneath the graphene channel is etched and the graphene is suspended over Si layer. However, the working principle of a GVT is completely different from that of the latter. The switching between ON and OFF states of a GBBGFET is achieved by tuning the conductance of the graphene channel through the voltage applied to the back gate. In a GVT, a graphene suspended between two metal electrodes works as the electron emitter. While one electrode is grounded (ground electrode), the other electrode acts as the gate (while it acts as the drain in a GBBGFET). The highly doped Si layer under the graphene emitter works as the collector (while it acts as the gate in a GBBGFET) and the space between the graphene emitter and the Si collector acts as the vacuum channel for electron transport. Our previous works have shown that, while the bias voltage applied to a graphene nanoribbon or a carbon nanotube is larger than a threshold value, significant electrons will emit laterally from it and emission current increases exponentially with the bias voltage. [22,23] This electron emission behavior

**Figure 1.** a,c) Schematic 3D and b,d) cross-sectional structures of a GVT (a, b) and a GBBGFET (c, d), indicating the analogous structures between them. The arrows indicate the movement of carriers.

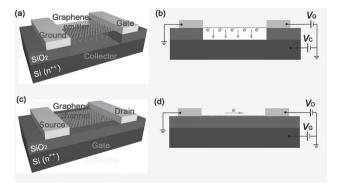

Figure 2. a) Global SEM image of a GVT. b) Local SEM image of the center part of a GVT (the framed area in (a)). c) Raman spectrum of a monolayer graphene emitter. Inset: Optical microscope image of the graphene taken before device fabrication.

is found to take place in graphene as well, and enables us to control the states of a GVT through the potential of the gate in Figure 1a. When the gate potential is below the threshold value, there is no electron emission from the graphene emitter and the GVT is in the OFF state; when the gate potential is high enough to drive significant electron emission from the graphene emitter, the GVT is switched ON. Since the emission current from the graphene emitter of a GVT is determined by the amplitude of the bias voltage applied to it or the potential difference between gate and ground electrodes without dependence on the polarity of the gate electrode potential, [22,23] the turn-on threshold potential of the gate electrode can be well controlled by tuning the electric potential of the ground electrode. This is a distinct feature of GVTs compared to previously reported transistors, [2,7,10,11,19,21] and may enable some novel applications.

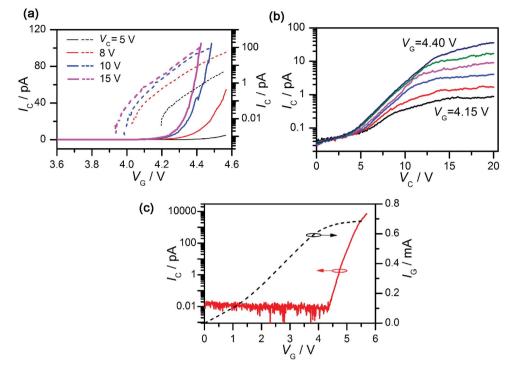

Figure 2a shows a global scanning electron microscope (SEM) image of a GVT. It has three square electrodes: gate, collector, and ground. While gate and ground electrodes are metal electrodes fabricated on the SiO2 dielectric layer, the collector electrode is heavily doped Si with the SiO<sub>2</sub> dielectric layer etched way. A magnified SEM image of the center part of the GVT in Figure 2b shows that a rectangular graphene emitter is suspended across a trench between the gate and ground electrodes and over the bottom Si collector. Figure 2c shows a Raman spectrum of the graphene emitter of the GVT, indicating its monolayer character. The transfer characteristics ( $I_C$ – $V_C$ curves) of a GVT with 2.0 µm long and 0.8 µm wide monolayer graphene emitter at different collector voltages ( $V_{\rm C}$ ) are shown in Figure 3a. It can be seen from the curves plotted in linear scale that, when gate voltage  $(V_G)$  is less than a threshold voltage of ≈4.1 V, there is no obvious electron emission from the graphene emitter and the GVT is in OFF state. When  $V_G$  is larger than the threshold voltage, emission current measured by the collector electrode (I<sub>C</sub>) increases rapidly with gate voltage and the GVT is switched on. The  $I_C$ – $V_G$  curves plotted in exponential

Figure 3. a) Transfer characteristics ( $I_C$ – $V_C$  curves) and b) output characteristics ( $I_C$ – $V_C$  curves) of a GVT with a monolayer graphene emitter at different collector voltages and different gate voltages. The solid and dashed lines in (a) are plotted in linear and exponential scale, respectively. b) Output characteristics corresponding to gate voltages increasing from 4.15 to 4.40 V at 0.05 V intervals. c) Transfer characteristics of another GVT when  $V_C$  = 15 V, showing an ON/OFF current ratio up to 10<sup>6</sup>. The  $I_C$ – $V_C$  curve of the GVT is also shown by a dashed line.

scale indicate that  $I_C$  increases exponentially with  $V_G$  above the threshold voltage and the GVT exhibits a ON/OFF current ratio as high as  $10^5$  and a subthreshold slope of  $\approx 120$  mV dec<sup>-1</sup>. The latter is close to the limit of the subthreshold slope of MOS FETs at room temperature (≈60 mV dec<sup>-1</sup>). The turn-on threshold voltage is found to decrease slightly with the increase of  $V_{\rm C}$ , while the subthreshold slope shows no obvious dependence on  $V_{\rm C}$ . The output characteristics ( $I_{\rm C}$ - $V_{\rm C}$  curves) of the monolayer GVT at different gate voltages are shown in Figure 3b. It can be seen that  $I_C$  increases nonlinearly with  $V_C$ , exhibiting a faster increasing regime followed by a slower increasing one at high V<sub>C</sub>. The movement of the suspended graphene emitter toward to the collector electrode due to the electrostatic pull of  $V_C$  is estimated to be negligible compared to the distance between them (see the Supporting Information), indicating that GVTs exhibit good mechanical stability.

The low ON/OFF current ratio of graphene FETs is attributed to the large OFF state current. In GVTs, the ON/OFF switching is based on electron emission from the emitter tuned by gate voltage. When gate voltage is smaller than the turn-on threshold voltage, there is no emission current from the emitter, which ensures an extremely small OFF current and allows us to achieve large ON/OFF current ratio if remarkable emission current at ON state is obtained. For a graphene emitter with a dimension of 1  $\mu m \times 2 \ \mu m$ , we obtained a maximum emission current up to 7.2 nA (corresponding to an emission current density of 0.36 A cm $^{-2}$ ) before it broke down due to severe electrical current and/or thermal stress, and an ON/OFF current ratio up to  $10^6$  and a subthreshold slope of  $\approx 150 \ mV \ dec^{-1}$  were obtained (Figure 3c). The transconductance of the GVT

was determined to be 15 nS  $\mu$ m<sup>-1</sup> at  $V_G = 5.6$  V and  $V_C = 15$  V by considering a channel width of 2 µm. The high ON/OFF current ratio and the low subthreshold slope indicate that GVTs exhibit exceptional ON/OFF switching performances. According to our previous studies, [22,23] the emission current from a graphene emitter at ON state increases with the surface area of the emitter (also see Figure S2, Supporting Information) and its increase with the bias voltage is basically related to the increase with the amplitude of internal electric field caused by the bias voltage. It means that, the ON/OFF current ratio of a GVT can be further increased by increasing the surface area of the graphene emitter and its subthreshold slope can be further reduced by decreasing the emitter width or the distance between the gate and ground electrodes. Therefore, the switching performances of GVTs can be further improved by optimizing the dimensions of the graphene emitters.

To compare the performances of GVTs with those of typical solid-state transistors based on graphene and on-chip vacuum transistors, their ON/OFF current ratio, subthreshold slope, transconductance and ON state current at room temperature are listed in **Table 1**. Due to the lack of a bandgap, intrinsic monolayer graphene FETs exhibit an ON/OFF current ratio of less than 10.<sup>[1,2]</sup> By opening a small bandgap in bilayer graphenes through applying a vertical electric field, the ON/OFF current ratio of dual-gate bilayer graphene FETs can reach  $10^{2}$ . FETs based on sub-10 nm wide graphene nanoribbons were demonstrated to exhibit the best switching performances among all intrinsic graphene-based solid-state transistors with an ON/OFF current ratio up to  $10^{6}$  and a subthreshold slope of 210 mV dec<sup>-1</sup>.<sup>[3]</sup> In addition to conventional FETs, several

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

**Table 1.** Comparison of the performances of GVTs with those of graphene-based solid-state transistors and on-chip vacuum transistors with working voltages of less than 10 V.

| Device types                                                       | ON/OFF current ratio | Subthreshold slope $[mV dec^{-1}]$ | Transconductance $[\mu S \ \mu m^{-1}]$ | ON current<br>[μΑ]           |

|--------------------------------------------------------------------|----------------------|------------------------------------|-----------------------------------------|------------------------------|

| Monolayer graphene FETs <sup>[2,26]</sup>                          | <10[2,26]            |                                    | 2000 <sup>[26]</sup>                    | 5000 <sup>[26]</sup>         |

| Dual-gate bilayer graphene FETs <sup>[2]</sup>                     | 10 <sup>2</sup>      |                                    |                                         | ≈1                           |

| Sub-10 nm graphene nanoribbon FETs <sup>[3]</sup>                  | 10 <sup>6</sup>      | 210                                | 900                                     | 4                            |

| Graphene barristors <sup>[10]</sup>                                | 105                  | ≈700                               |                                         | ≈1                           |

| Graphene-based hot electron transistors <sup>[11]</sup>            | 105                  | ≈140                               |                                         | $\approx 1.7 \times 10^{-2}$ |

| Graphene/WS $_2$ /graphene vertical tunneling transistors $^{[7]}$ | 10 <sup>6</sup>      | 2200                               |                                         |                              |

| MOS FETs with vacuum channel <sup>[21]</sup>                       | $5 \times 10^2$      |                                    | 0.02                                    | ≈0.1                         |

| Gate insulated vacuum channel transistors <sup>[19]</sup>          | 10 <sup>6</sup>      | 4200                               |                                         | ≈20                          |

| GVTs                                                               | 10 <sup>6</sup>      | 120                                | 0.015                                   | $7.2 \times 10^{-3}$         |

new conceptual graphene-based devices have been proposed to realize high ON/OFF current ratio. Graphene barristors based on gate-controlled graphene/silicon Schottky barrier were reported to exhibit a high ON/OFF current ratio of 105, but a large subthreshold slope of  $\approx$ 700 mV dec<sup>-1</sup>.[10] Vertical graphene-based hot electron transistors were found to have an ON/OFF current ratio of exceeding 105 and a subthreshold slope of ≈140 mV dec<sup>-1</sup>.<sup>[11]</sup> Vertical field-effect tunneling transistors based on graphene/WS2/graphene were reported to have an ON/OFF current ratio of exceeding 106, but only a large subthreshold slope of 2200 mV dec<sup>-1</sup> was experimentally demonstrated.<sup>[7]</sup> By comparing the ON/OFF current ratio and subthreshold slope of our GVTs with those of the graphene-based solid-state transistors, it can be seen that the switching performances of GVTs are superior to those of previously reported graphene-based solid-state transistors.

To scale down the size of traditional vacuum electronic devices and realize vacuum microelectronics, many efforts have already been made to develop on-chip microscale vacuum transistors using semiconductor microfabrication technology. However, the performances of those microscale vacuum transistors are still overshadowed compared to those of solid-state ones. Previously reported on-chip vacuum transistors are exclusively based on field emission and many materials, e.g., carbon nanotubes,[13-15] metal tips,[17] Si tips,[18] etc., have been used as the field emitters. Due to the intense electric field needed to enable field emission. field emission vacuum triodes/transistors generally need high working voltages up to at least tens of volts, which are much higher than those of many solid-state devices. As shown in Figure 3, our fabricated GVTs can work at low voltages of less than 10 V, comparable to those of graphene-based solid-state devices. [3,4,10-12] Recently, two field emission vacuum transistors in novel designs, vacuum channel MOS FETs and gate insulated vacuum channel transistors,[19-21] were reported to exhibit low working voltages of less than 10 V. However, their switching performances are still unsatisfactory. Vacuum channel MOS FETs exhibited an ON/OFF current ratio of only 500.[21] Even though the ON/OFF current ratio of gate insulated vacuum channel transistors reaches up to 106, they have a large subthreshold slope of 4200 mV dec<sup>-1</sup>.[19] In contrast to the unsatisfactory switching performances of those field emission vacuum transistors, our GVTs possess both comparable working voltages and superior switching performances when compared to graphenebased solid-state transistors, which may overturn our traditional knowledge that the performances of vacuum devices are inferior to those of solid-state ones. The exceptional performances of GVTs are basically attributed to the special electron emission properties of graphene emitters. The mechanism responsible for the electron emission from the graphene emitters is thought to be phonon-assisted electron emission under electrical drive, in which internal electric field, in addition to the effect of Joule heating, contributes directly to the electron emission. [22,25] While self-Joule heating is a relatively slow process that may limit the switching speed of GVTs, the electron emission mainly triggered by internal electric field ensures that the triggering mechanism for electron emission is not a limiting factor for the switching speeds of GVTs. To the best of our knowledge, this is the first demonstration of on-chip microscale vacuum transistors based on the mechanism other than field emission.

While GVTs exhibit exceptional ON/OFF current ratio and subthreshold slope, they still perform unsatisfactorily in some other aspects including transconductance, ON state current and power efficiency when compared with those of the solidstate transistors based on graphene. The transconductance of the GVT shown in Figure 3c is 15 nS µm<sup>-1</sup>. Even though it is comparable with the transconductance of MOS FETs with vacuum channel,[21] it is about five orders of magnitude smaller than those of the FETs based on epitaxial graphene grown on SiC substrates and sub-10 nm graphene nanoribbons. [3,26] Since the voltage gain of a transistor is proportional to its transconductance, the low transconductance of GVTs may limit their applications as amplifiers. Another shortage of GVTs is their small ON state current of a few nA (Figure 3c). Even though it is comparable with the ON state current of graphene-based hot electron transistors, [11] it is much smaller than the ON state current of other graphene-based solid-state transistors listed in Table 1 as well as those of the on-chip vacuum transistors. Therefore, GVTs are expected to have a relatively large intrinsic delay time since it is inversely proportional to the ON state current, and they may perform poor in high-frequency applications due to the slow switching speed. The power efficiency of transistors is also a highly concerned problem. As shown in Figure 3c, the current passing through the gate electrode ( $I_C$ ) of the GVT in the ON state is as high as ≈0.7 mA, which is

5975

www.MaterialsViews.com

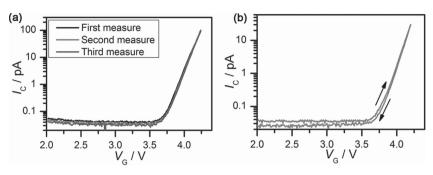

Figure 4. Transfer characteristics of a GVT a) measured repeatedly and b) in dual-direction when  $V_{\rm C}=15$  V.

much larger than the collector current. So, the high ON/OFF current ratio of GVTs is obtained in the expense of power efficiency. The improvements in transconductance, ON state current, and power efficiency can be achieved by increasing emission current from the graphene emitters through the methods including increasing graphene emitter area (Figure S2, Supporting Information), and decreasing the work function of graphene by chemical doping.

Figure 4 shows the transfer characteristics of a GVT measured repeatedly and in dual direction. It can be seen from Figure 4a that, the GVT exhibits highly repeatable transfer characteristic curves for three different measurements. The repeatable transfer characteristics are attributed to stable electron emission from the graphene emitter. Compared to the

field electron emission from a sharp tip under extremely high local electric field of ≈1 V nm<sup>-1</sup>, which usually exhibits fluctuating emission current due to the fluctuation of work function caused by the absorption and desorption of residual molecules and the local changes of emitter tip microstructures,[27] high stability of graphene honeycomb lattice, low collecting electric field of only ≈0.1 V nm<sup>-1</sup>, and low residual molecule absorption to the hot Joule-heated graphene emitters ensure highly stable electron emission from the graphene emitter, and thus stable transfer characteristics of a GVT. In previously reported solid-state and vacuum transistors, the conductance of the channels is tuned by capacitively coupled gate electrodes, so their transfer characteristics exhibit hysteresis if there are trapped charges at the interfaces between channel and gate electrodes.<sup>[28]</sup> In our proposed GVTs, the conductance of vacuum channels is tuned by the bias voltage applied to the graphene emitter through a gate directly contacting with it. Since the threshold voltage for electron emission is an intrinsic property of the emitter itself and is insensitive to the trapped charges at the interfaces of the devices, the transfer characteristics of our GVTs is nearly free of hysteresis as shown in Figure 4b. The highly repeatable and hysteresis-free transfer

characteristics indicate that our GVTs exhibit stable switching performances.

The fabrication of GVTs with silicon microfabrication technology makes it possible to achieve more advanced device functions by integrating GVTs just like the integration of MOS FETs, which is of great importance for realizing vacuum integrated circuits. Field-effect devices with ambipolar transfer characteristics have been demonstrated to show great potential in AC applications and can work as frequency multipliers, in-phase and inverted amplifiers, etc.<sup>[29,30]</sup> Here, to demonstrate the integration of

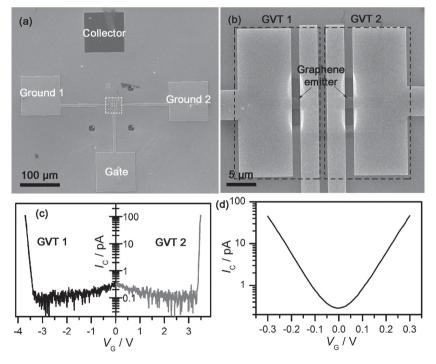

GVTs, we have fabricated an ambipolar device with perfectly symmetric ambipolar transfer characteristics by integrating two GVTs. **Figure 5**a,b shows the SEM images of a graphene-based vacuum ambipolar device, which consists of two GVTs (GVT 1 and GVT 2) with shared gate and collector electrodes (Figure 5a). The transfer characteristics of GVT 1 and GVT 2 are shown in Figure 5c when they work separately. It can be seen that GVT 1 and GVT 2 have a turn-on threshold voltage of 3.40 and 3.33 V, respectively. A distinct feature of GVTs is that the turn-on threshold potential of the gate electrode can be welled controlled by tuning the electric potential of the ground electrode. If the electric potential of the ground electrode of GVT 1 is set to be 3.40 V, then the threshold gate potential for the electron emission from its emitter is shifted to 0 V and

**Figure 5.** a) Global SEM image of an ambipolar device by integrating two GVTs with shared gate and collector electrodes. b) Enlarged SEM image of the framed area in (a), showing that two GVTs (GVT 1 and GVT 2) are integrated in the ambipolar device in (a). c) Transfer characteristics of GVT 1 and 2 in (b) when they work separately at  $V_C = 15$  V. d) Transfer characteristics of the ambipolar device in (a) when  $V_C = 15$  V and electric potential of the ground electrode 1 and 2 is set to be 3.40 and -3.33 V, showing perfectly symmetric ambipolar characteristics.

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

there is significant electron emission for a negative gate potential. Similarly, if the electric potential of the ground electrode of GVT 2 is set to be -3.33 V, the threshold gate potential for the electron emission from its emitter is also shifted to 0 V, but there is significant electron emission for a positive gate potential. Therefore, when electric potential of the ground electrodes of GVT 1 and GVT 2 is set to be 3.40 and -3.33 V, respectively, for the integrated device shown in Figure 5a, the collector electrode will detect emission current for both negative and positive gate potential and emission current increases exponentially with the increase of the amplitude of the gate potential. A perfectly symmetric ambipolar transfer characteristic centered at 0 V as shown in Figure 5d is thus obtained. If a sinusoidal AC potential with a frequency of  $\omega$  is input to the gate electrode, an AC current with a frequency of  $2\omega$  can be collected by the collector electrode. So the ambipolar device works as a frequency doubler if it works in AC mode. The successful realization of the ambipolar device by integrating two GVTs, together with exceptional switching performances of individual GVTs shown in Figures 3 and 4, implies the potential of achieving both logic and AC functions in a GVT-based vacuum integrated circuit. The batch fabrication and large-scale integration of GVTs for vacuum integrated circuits could be achieved by using waferscale large area graphene samples.

#### 3. Conclusion

In conclusion, a GVT is proposed and experimentally demonstrated to have an ON/OFF current ratio up to 106 and a subthreshold slope of 120 mV dec-1, exhibiting switching performances superior to those of previously reported graphenebased solid-state transistors. Furthermore, GVTs have low working voltages comparable to those of graphene-based solidstate transistors, and can be fabricated and integrated using the silicon microfabrication technology. By integrating two GVTs, an ambipolar device with perfectly symmetric transfer characteristics is realized. The competitive performances of GVTs compared to those of graphene-based solid-state devices make GVTs a new potential candidate for post-CMOS devices and may induce a re-evaluation of the future of vacuum electronic devices. As vacuum transistors, GVTs are expected to find applications in extreme environments such as high temperature and intense irradiation as switches, rectifiers, and frequency doublers.

### 4. Experimental Section

Graphene-based vacuum transistors were fabricated using silicon microfabrication technology in a process similar to that of graphene-based back-gate FETs. Graphene films on a SiO<sub>2</sub>/Si wafer were first obtained by mechanical exfoliation of a thin foil of highly oriented pyrolytic graphite. SiO<sub>2</sub>/Si wafers with a SiO<sub>2</sub> layer thickness of 300 nm were used. The obtained graphene films were then carefully examined under an optical microscope to look for monolayer or bilayer graphene for further device fabrication. The layer number of graphene films was determined through the contrast of optical microscope imaging. Some graphene films were further examined by taking Raman spectra to unambiguously determine their layer number. After proper graphene films were selected, they were tailored to graphene ribbons in

predesigned dimensions by electron beam lithography (EBL) followed by plasma etching. 70 nm Au/5 nm Cr electrodes were then deposited on the graphene ribbons using standard EBL, metal film deposition, and lift-off processes. To etch the  $\mathrm{SiO}_2$  layer underneath the graphene ribbons, an additional EBL step was carried out to open a small window in polymethyl methacrylate (PMMA) mask for chemical etching, and then the silicon wafer was immersed in buffered hydrofluoric acid. After removing the PMMA mask and drying the wafer in hot isopropanol, GVTs with a graphene suspended between two metal electrodes are finally obtained. The performances of GVTs are tested on a probe station at room temperature and a vacuum level of  $10^{-2}$ – $10^{-3}$  Pa by using a Keithley 4200 semiconductor characterization system.

# **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

## Acknowledgements

This work was supported by the National Basic Research Program of China (Grant No. 2013CB933604), NSF of China (Grant Nos. 61371001, 11304003, and 61321001), the Foundation for the Author of National Excellent Doctoral Dissertation of China (Grant No. 201241), and the Specialized Research Fund for the Doctoral Program of Higher Education of China (Grant No. 20130001110030). X.W. also thanks the support of the State Key Laboratory of Optoelectronic Materials and Technologies (Sun Yat-sen University).

Received: May 18, 2015 Revised: July 25, 2015 Published online: August 21, 2015

- K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, A. A. Firsov, Science 2004, 306, 666.

- [2] F. Xia, D. B. Farmer, Y. M. Lin, P. Avouris, Nano Lett. 2010, 10, 715.

- [3] X. Wang, Y. Ouyang, X. Li, H. Wang, J. Guo, H. Dai, Phys. Rev. Lett. 2008, 100, 206803.

- [4] M. W. Lin, C. Ling, Y. Zhang, H. J. Yoon, M. M. C. Cheng, L. A. Agapito, N. Kioussis, N. Widjaja, Z. Zhou, Nanotechnology 2011, 22, 265201.

- [5] B. N. Szafranek, D. Schall, M. Otto, D. Neumaier, H. Kurz, *Nano Lett.* 2011, 11, 2640.

- [6] B. N. Szafranek, D. Schall, M. Otto, D. Neumaier, H. Kurz, Appl. Phys. Lett. 2010, 96, 112103.

- [7] T. Georgiou, R. Jalil, B. D. Belle, L. Britnell, R. V. Gorbachev, S. V. Morozov, Y. J. Kim, A. Gholinia, S. J. Haigh, O. Makarovsky, L. Eaves, L. A. Ponomarenko, A. K. Geim, K. S. Novoselov, A. Mishchenko, *Nat. Nanotechnol.* 2013, 8, 100.

- [8] L. Britnell, R. V. Gorbachev, R. Jalil, B. D. Belle, F. Schedin, A. Mishchenko, T. Georgiou, M. I. Katsnelson, L. Eaves, S. V. Morozov, N. M. R. Peres, J. Leist, A. K. Geim, K. S. Novoselov, L. A. Ponomarenko, *Science* 2012, 335, 947.

- [9] N. Myoung, K. Seo, S. J. Lee, G. Ihm, ACS Nano 2013, 7, 7021.

- [10] H. Yang, J. Heo, S. Park, H. J. Song, D. H. Seo, K. E. Byun, P. Kim, I. Yoo, H. J. Chung, K. Kim, *Science* 2012, 336, 1140.

- [11] C. Zeng, E. B. Song, M. Wang, S. Lee, C. M. Torres Jr., J. Tang, B. H. Weiller, K. L. Wang, *Nano Lett.* **2013**, *13*, 2370.

- [12] S. Vaziri, G. Lupina, C. Henkel, A. D. Smith, M. Östling, J. Dabrowski, J. Lippert, W. Mehr, M. C. Lemme, *Nano Lett.* 2013, 13, 1435.

www.afm-iournal.de

www.MaterialsViews.com

- [13] C. Bower, D. Shalom, W. Zhu, D. López, G. P. Kochanski, P. L. Gammel, S. Jin, IEEE Trans. Electron Dev. 2002, 49, 1478.

- [14] Y. M. Wong, W. P. Kang, J. L. Davidson, B. K. Choi, W. Hofmeister, J. H. Huang, Diam. Relat. Mater. 2005, 14, 2069.

- [15] J. Wu, M. Wyse, D. McClain, N. Thomas, J. Jiao, Nano Lett. 2009, 9,

- [16] S. H. Hsu, W. P. Kang, S. Raina, J. H. Huang, Appl. Phys. Lett. 2013, 102, 203105.

- [17] C. A. Spindt, C. E. Holland, A. Rosengreen, I. Brodie, IEEE Trans. Electron Dev. 1991, 38, 2355.

- [18] L. Pescini, A. Tilke, R. H. Blick, H. Lorenz, J. P. Kotthaus, W. Eberhardt, D. Kern, Adv. Mater. 2001, 13, 1780.

- [19] J. W. Han, J. S. Oh, M. Meyyappan, Appl. Phys. Lett. 2012, 100, 213505.

- [20] J. W. Han, J. S. Oh, M. Meyyappan, IEEE Trans. Nanotechnol. 2014,

- [21] S. Srisonphan, Y. S. Jung, H. K. Kim, Nat. Nanotechnol. 2012, 7, 504.

- [22] X. L. Wei, D. Golberg, Q. Chen, Y. Bando, L. M. Peng, Nano Lett. 2010, 11, 734.

- [23] X. L. Wei, Y. Bando, D. Golberg, ACS Nano 2011, 6, 705.

- [24] Z. H. Ni, T. Yu, Z. Q. Luo, Y. Y. Wang, L. Liu, C. P. Wong, J. Miao, W. Huang, Z. X. Shen, ACS Nano 2009, 3, 569.

- [25] X. L. Wei, D. Golberg, Q. Chen, Y. Bando, L. M. Peng, Phys. Rev. B **2011**, *84*, 195462.

- [26] Y. Q. Wu, D. B. Farmer, A. Valdes-Garcia, W. J. Zhu, K. A. Jenkins, C. Dimitrakopoulos, P. Avouris, Y.-M. Lin, in IEDM Tech. Dig., IEEE, Piscataway, NJ 2011, 23.8.1.

- [27] N. de Jonge, J. M. Bonard, Philos. Trans. R. Soc. London A 2004, 362, 2239.

- [28] H. Wang, Y. Wu, C. Cong, J. Shang, T. Yu, ACS Nano 2010, 4, 7221.

- [29] Z. X. Wang, L. Ding, T. Pei, Z. Y. Zhang, S. Wang, T. Yu, X. F. Ye, F. Peng, Y. Li, L. M. Peng, Nano Lett. 2010, 10, 3648.

- [30] Z. X. Wang, Z. Y. Zhang, H. Zhong, T. Pei, S. B. Liang, L. Yang, S. Wang, L. M. Peng, Adv. Funct. Mater. 2013, 23, 446.